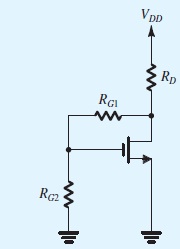

Problem:

1. Figure shows a variation of the feedback-bias circuit of Figure. Using a 5-V supply with an NMOS transistor for which Vt = 0.8 V, kn = 8 mA/V2, and λ=0, provide a design that biases the transistor at ID =1 mA, with VDS large enough to allow saturation operation for a 2-V negative signal swing at the drain. Use 22MΩ as the largest resistor in the feedback-bias network. What values of RD, RG1, and RG2 have you chosen? Specify all resistors to two significant digits.